急速驰骋 十款GDDR5显卡全接触

一起来认识GDDR5显存

频率是存储器为显著的特征。目前GDDR3的数据传输频率高可以达到2600MHz,相比之下,目前GDDR5可以达到5000MHz。不过这依旧不是终点,GDDR5高数据传输频率将达到6000MHz。和之前几代GDDR显存一样,GDDR5也是建立在多倍数据预取技术上的产品。根据显存发展的历史来看,GDDR1显存采用2bit数据预取技术,GDDR2、GDDR3和GDDR4都采用了4bit数据预取技术,GDDR5正是新一代8bit数据取技术的产物,达到了令人惊异的高性能。

优秀的双总线设计—高速传输无忧

相比GDDR3采用的4bit预取数据而言,GDDR5的优势在于将预取数据增加到了8bit,因此GDDR5就能够在同样的物理时钟频率下达到更高的数据传输速度。不仅如此,GDDR5显存采用了双数据总线,能够同时在数据总线的上升和下降阶段传输数据。同时,每条总线都独立配备了完整的DBI,可以独立传输、校验数据,是完整的双总线规格。以往单数据总线的GDDR2、GDDR3等显存标称频率是等效工作频率的1/2(比如标称频率为900MHz的GDDR3显存,等效工作频率为1800MHz),而GDDR5显存由于双总线技术的存在,每条总线都可以在上升和下降阶段传输数据,因此标称频率是等效工作频率的1/4。以4000MHz等效工作频率的GDDR5显存为例,它的标称频率为1000MHz。由于采用了8bit的预取技术,因此它的实际物理运行频率为125MHz。

GDDR显存几种频率的差别

物理运行频率:是指GDDR显存实际运行的物理频率,这个频率可以在主板上用仪器实际测得。在通常的使用中,物理运行频率是极少被提及的。

标称频率:由于采用了多倍预取技术,因此GDDR显存的标称频率远远高于物理运行频率。以GDDR3为例,它采用4bit预取,因此物理运行频率为250MHz的GDDR3显存,标称频率就为1000MHz。在GPU-Z、Rivatuner等软件的截图中,看到的显存频率就是标称频率。

等效工作频率:等效工作频率是GDDR显存衡量实际传输数据能力的频率。一般GDDR2、GDDR3、GDDR4等单总线显存的等效工作频率是标称频率的2倍。而GDDR5采用了双总线技术,因此等效工作频率是标称频率的4倍。我们经常看到厂商和大部分媒体宣传的显存频率实际就是等效工作频率,这也是大家使用广泛、认知度高的GDDR显存频率。另外,等效工作频率可以直接和显存位宽相乘进行计算。比如等效工作频率为2000MHz的GDDR3显存,如果显存的位宽为128bit,那么总显存带宽就是2000MHz×128bit÷8=32GB/s。

稳定+节能,其实很简单—Data eye optimization数据核心优化

对于数据的优化是存储器为重要的方面,GDDR5重点采用了四项技术来保证数据的稳定性和安全性。Data/address bit inversion,即数据/地址位反演是指在传输过程中,数据或者地址位内的信息被按照一定的规则做了反演处理。数据/地址位反演技术的作用在于有效地改善了噪音对数据信号的影响,保证了数据在传输和存储过程中的稳定性。不难看出,数据/地址位反演技术是GDDR5在传输中重要的处理技术,也是降低功耗和提高数据稳定性的首要法宝。

除了数据/地址位反演技术外,三项动态调节技术:adjustable driver strengths、adjustable voltages和adjustable terminations也是GDDR5数据核心优化的重要组成部分。它们分别针对驱动器、电压和终止装置进行自动调节。在传统的显存数据传输过程中,由于显存并行传输的特性,对线长和外界干扰有着严格的规定。因此我们常常在显存周围看到大量的密密麻麻的终结电阻(减少反射损耗)等元件,显卡不得不在显存周围采用蛇形走线来尽可能做到信号线等长。但在GDDR5上这些严格的要求被弱化了,GDDR5自带的调节系统可以在一定范围内保证数据信号在高速运行时不出错,甚至信号线都可以不用严格等长。除了更宽松的信号传输空间外,GDDR5对电压和温度的动态调节和实时监控,也使得整个信号在传输过程中的安全性更高。另外,工程人员可以在BIOS中写入设定好的调整信息,避免在PCB已经正式出样(layout)之后由于信号稳定性问题导致返工。

如何识别GDDR5显存

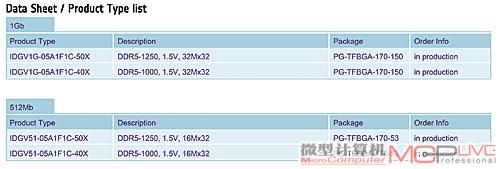

目前已经上市的GDDR5显存拥有两种速度规格和两种容量规格,可选择余地并不多。以市场常见的奇梦达GDDR5显存为例,分为-40X和-50X两种,分别对应4.0Gbps和5.0Gbps的传输速率,即理论上它们的等效工作频率为4000MHz和5000MHz。尚未上市的现代和三星GDDR5显存分类则更细,拥有3500MHz、4000MHz、4500MHz和5000MHz等多种频率规格。

编号为奇梦达IDGV51-05A1F1C-40X的GDDR5显存

奇梦达GDDR5显存规格列表

安全+自由,放心传数据—Adaptive interface timing时钟自适应技术

信号线和时钟稳定性是高速显存设计中重要的部分。GDDR5显存拥有多达5条需要校准的时钟信号,分别是Clock、Command Clock、ADDR、Write Clock、DATA Clock时钟信号。在高速运行的情况下(诸如高达2GHz),任何一点微小的差距都会带来整个系统的数据错误、崩溃。因此,GDDR5在时序自动校准、自适应技术上已经有了一套非常完整的方案,能够带来非常高的数据运行效率。

首先,GDDR5会要求地址时钟和总线时钟(ADDR和CK#)进行对照并对齐。实际上这是在进行一次芯片的初始化,在此阶段控制器可以找到佳的相位设置。接下来就需要校准Write Clock(WCK)和基准Clock(CK#)之间的数据,这个过程被称为“WCK-to-CK”。在这个过程中,控制器可以找出WCK和CK#之间相位的差距,是“早”还是“迟”,然后为每一个DRAM给出相应的调节数据。后,控制器会调整数据总线(DATA和WCK)。由于数据总线DATA的频率是WCK写入时钟的2倍,因此每次校准会涉及到两个字节。

GDDR5的这种校准方法,使得整个数据线环环相扣,降低了由于时钟不同步带来的数据错误或系统延迟,也在很大程度上降低了PCB设计的难度。由于有内部校准机制的存在,工程师们在PCB布线的一致性方面就有了更宽松的空间,这让整个PCB的布线更为自由和宽松。

另外,更为自由的数据预取技术也让GDDR5在图形应用中充满了优势。在图形计算中存在大量密集而微小的数据,这些数据甚至会小于GDDR5每次预取的低数据。如果采用固定的预取值的设计方法,即每次无论数据大小(甚至使用空位)都一定要完全占据传输总线,无疑会耗费很多能量。因此,GDDR5允许小于预取数量的数据传输,即采用低预取方式。这种灵活的设计,让GDDR5在传输大量小数据量运作时,功耗有明显的降低。

GDDR5的折叠模式

大多数的单颗GDDR显存位宽均为32bit,GPU如果是128bit的显存位宽,就需要4颗显存就可以使位宽相互匹配。但如果显卡要使用8颗显存形成更大容量的话,就需要相应的GPU显存控制器支持双BANK读写才可完成,灵活度不够高。而GDDR5显存内置双数据总线,32bit的显存可以轻松拆分为16bit颗粒使用,不需要GPU的额外支持也可以使显存容量翻倍。这种设计简化了GPU的显存控制器,增加了用户选择的自由度。

纠错+校验,完美保传输—Error compensation误差补偿技术

由于电磁环境或者传输中温度、电压等复杂因素的影响,显存在数据传输和存储过程中可能会产生少量的错误——一个简单的显存数据错误除了导致渲染失败以外,还可能导致显卡彻底失去响应、蓝屏和系统崩溃等严重问题。因此对错误数据的校验和补偿,成为GDDR5瞄准的又一个重要目标。

GDDR5的数据校验采用了CRC(Cycle Redundancy Check循环冗余校验)方式。CRC校验是建立在GDDR5的DATA I/O和DBI的基础上,如 果出现错误,则触发数据传输总线,然后快速重新读取数据,或者利用如Data Mask(数据掩蔽)等功能修改数据并重新传输。这种校验方式的优势在于能够100%检测出所有单、双数据误差。

Data Mask(数据掩蔽)是这样一项技术:GDDR5显存在每次读写数据时,并不是改写所有的数据,大部分数据都不需要修改。因此GDDR5利用地址总线对一部分数据进行掩蔽,在下一次数据读写到来时,仅仅对没有掩蔽的数据进行更改。这样就能在快的时间内完成数据读写。